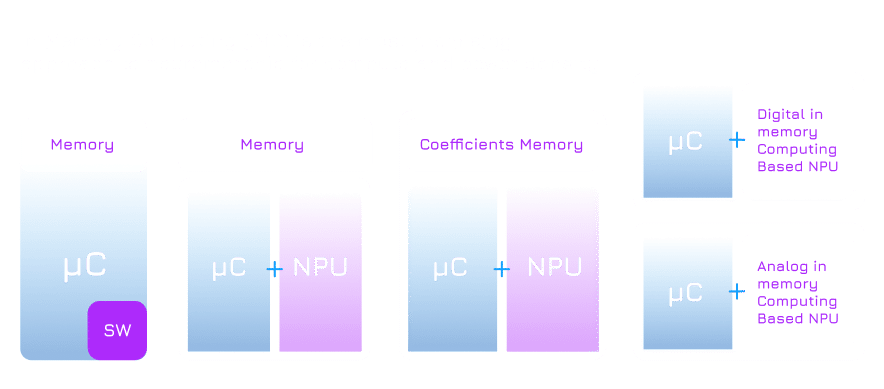

In Memory Computing approaches

Memory centric architectures can

be associated to many topologies

Two broad classifications of IMC apply: DIMC (Digital In Memory Compute) and AIMC (Analog In memory Compute)

In the case of DIMC the computation happens in the memory spread across the single memory bit cell and a group of bit cells that can be accessed in parallel to perform an accumulation operation. This deterministically generates a precise bit accurate output.

The AIMC architectures are associated to cases where the computation happens by way of an analog operation such as a current summation or charge transfer either in a column wise or a row wise fashion with an analog and digital conversion at the end to generate the final output

In NeuroSoC the focus will be on AIMC.

Objectives

Detailed technical objectives

- Design of a PCM computational memory tile for AIMC in 28nm FD-SOI technology

- Design of a SRAM computational memory tile for AIMC in 28nm FD-SOI technology complementing the PCM one for selected ultra-low cost and always on use-cases

- Design of a reusable and modular hybrid IMC based neural processing unit for scalable edge-AI SoCs

- Assessment and characterization of security exploits techniques for IMC based NPUs

- Enhancement of a RISC-V multicore microcontroller implementation to support functional safety

- Explore functional safety solutions for IMNPU IPs for industrial and automotive use cases

- Study and optimize AI Deep Learning algorithms optimized for IMC and selected use-cases

- Prototype IMC based AI tools and compilers for efficient mapping of deep learning algorithms

- Design of an advanced 28nm FD-SOI complete MPSoC integrating the technology developed in the project

- Validate use-cases to assess the benefits of the technology and tools developed in the project

NeuroSoC achievements after 12 Months

In the first year of the project, the focus of the work has been the definition of the hardware architecture and the various elements needed, with a special focus on the development of a PCM NVM memory capable to store multilevel values, and to perform In Memory Computing.

For the IMNPU unit, three distinct architectures, namely the router-based, cluster-based and 2D mesh-based architectures, were evaluated for their suitability for the targeted weight stationary system. More specifically, the architectures were assessed for design flexibility, scalability, performance/cost and power efficiency. Finally, the 2D mesh-based architecture was selected as a suitable candidate for NeuroSoC. Various approaches to schedule the data processing in the mesh architecture have been discussed with the conclusion that two schemes, the time scheduling approach and the data driven approach provide advantages for specific use cases. The evaluation of these approaches brought the conclusion that both approaches seem to have their advantages and disadvantages. Since the implementation of the required hardware support for both schemes is negligible, we decided to support both schemes and to provide the software tool chain with the freedom to use one or the other depending on the use case and better applicability. The initial version of the RISC-V component has been synthesized in various configurations.

Regarding the security aspects, two methods, the “Encoder-Decoder based approach” and the “Tile-by-Tile approach” have been successfully explored, showing potential security risks on the In-Memory Computing (IMC) based systems due to Side-Channel Attacks.

For the characterization of the PCM cell, a set of different type of cells have been considered, and two batches of standard and rheostatic cells have been fabricated and extensively characterized.

On these cells, a multilevel programming algorithm has been implemented. With the results obtained in the first period, the multilevel is working, but convergence is not always guaranteed. The algorithm and the convergence are under refinement. The computational accuracy of the Analog In Memory Computing based on PCM , and the comparison with the digital compute engine are under evaluation.

For the design of the AIMC tile, two architectures have been considered, one main architecture and one exploratory architecture, both starting from elements of existing tiles from IBM and ST.

A RTL design of the AIMC tile, to be integrated in the overall architecture, has been realized, and it is ready to be produced for the verification of the real hardware.

For the AIMC based on SRAM, a first test chip has been realized and it is currently under evaluation in terms of non idealities of the real hardware and effect of analog noise sources.

Finally a first version of the wrapper of the AIMC tiles in the main architecture has been defined.

Regarding the development of the software toolchain to be used to program the NeuroSoC system, based on the hardware architecture that has been depicted during the first year, the software stack components have been identified and connected in a proper structure, in order to allow the deployment of neural networks on the emulator first, and finally on the NeuroSoC device. In the first year the focus has been on the definition of the software architecture and the related simulations/emulation elements, taking into consideration the needs of the end user for the demonstration of efficiency and quality level requirements.

Based on the variety of applications considered, from automotive to aerospace, security and safety, the requirements of the target applications of the NeuroSoC device have been analyzed and the possibility of fulfillment of these requirements with the defined architecture has been confirmed.